domingo, 10 de octubre de 2021

sábado, 9 de octubre de 2021

CUESTIONARIO DE CLASE

¿QUÉ ES LA ELECTRÓNICA ?

Se llama electrónica a una disciplina técnica y científica, considerada como una rama de la física y como una especialización de la ingeniería, que se dedica al estudio y la producción de sistemas físicos basados en la conducción y el control de un flujo de electrones o de partículas cargadas eléctricamente.

Para ello, la electrónica se sirve no solo de ciertos principios teóricos básicos como el electromagnetismo, sino también de la ciencia de los materiales y otras formas de aplicación práctica del conocimientos científicos. Sus resultados son de especial interés para otros campos del saber especializado, como la informática o la ingeniería de sistemas.

Entre las aplicaciones contemporáneas de la electrónica se encuentran:

- Sistemas de control. Permiten poner en marcha o detener procesos, como es el caso de los circuitos de luz en nuestros hogares y pueden adquirir incluso cierto grado de automatización.

- Electrónica de potencia. Se basa en el empleo de dispositivos electrónicos para regular potencia y voltaje eléctrico, sobre todo a niveles significativos, lo cual es clave en la distribución de la energía y en otros procesos industriales contemporáneos.

- Telecomunicaciones. Es una de las áreas más amplias del desarrollo tecnológico de la electrónica tiene que ver con las base de datos y sistemas de información digital, como internet. Así como con el universo de gadgets o artefactos electrónicos disponibles para la llamada cultura 2.0.

Existen diferentes tipos de compuertas y algunas de estas son más complejas, con la posibilidad de ser simuladas por compuertas más sencillas. Todas estas tienen tablas de verdad que explican los comportamientos en los resultados que otorga, dependiendo del valor booleano que tenga en cada una de sus entradas.

¿QUÉ ES EL MAPA DE KARNAUGH?

La tabla de Karnaugh consiste en una representación bidimensional de la función que se quiere simplificar. Si la función viene expresada como una tabla de verdad, entonces la tabla de Karnaugh puede verse como una forma alternativa de representación 2D. Puesto que la tabla de verdad de una función de n variables posee 2n filas, la tabla de Karnaugh correspondiente debe poseer también 2n celdas. La construcción de la tabla de Karnaugh pasa por codificar cada celda en código binario reflejado (o código Gray) de manera que celdas adyacentes tengan un código que difiere en un solo dígito.

viernes, 8 de octubre de 2021

TIPOS DE DISPOSITIVOS LÓGICOS PROGRAMABLES.

Circuito

integrado de aplicación específica (ASIC)

Un

Circuito Integrado para Aplicaciones Específicas (o ASIC, por sus siglas en

inglés) es un circuito integrado hecho a la medida para un uso en particular,

en vez de ser concebido para propósitos de uso general. Se usan para una

función específica. Por ejemplo, un chip diseñado únicamente para ser

usado en un teléfono móvil es un ASIC. Por otro lado, los circuitos

integrados de la serie 7400 son circuitos lógicos (combinacionales o

secuenciales) que se pueden utilizar para una multiplicidad de aplicaciones. En

un lugar intermedio entre los ASIC y los productos de propósito general están

los Productos estándar para Aplicaciones Específicas, o ASSP por sus siglas en

inglés.

Con los avances en la miniaturización y en las herramientas de

diseño, la complejidad máxima, y por ende la funcionalidad, en un ASIC ha

crecido desde 5.000 puertas lógicas a más de 100 millones. Los ASIC

modernos a menudo incluyen procesadores de 32 bits, bloques de memoria RAM,

ROM, EEPROM y Flash, así como otros tipos de módulos. Este tipo de ASIC

suele ser llamado Sistema en un Chip, o SoC, por sus siglas en inglés. Los

diseñadores de ASIC digitales usan lenguajes descriptores de hardware (HDL),

tales como Verilog o VHDL, para describir la funcionalidad de estos

dispositivos.

Complex

Programmable Logic Device(CPLD)

Un CPLD (del acrónimo inglés Complex Programmable Logic Device)

es un dispositivo electrónico.

Los CPLD extienden el concepto de un PLD (del acrónimo inglés Programmable

Logic Device) a un mayor nivel de integración ya que permite implementar

sistemas más eficaces, ya que utilizan menor espacio, mejoran la fiabilidad del

diseño, y reducen costos. Un CPLD se forma con múltiples bloques lógicos, cada

uno similar a un PLD. Los bloques lógicos se comunican entre sí utilizando una

matriz programable de interconexiones, lo cual hace más eficiente el uso del

silicio, conduciendo a una mejor eficiencia a menor costo. A continuación se

explican brevemente las principales características de la arquitectura de un

CPLD.

Field

Programmable Gate Array(FPGA)

Una FPGA (del inglés Field Programmable Gate Array) es un

dispositivo semiconductor que contiene bloques de lógica cuya interconexión y

funcionalidad puede ser configurada 'in situ' mediante un lenguaje de

descripción especializado. La lógica programable puede reproducir desde

funciones tan sencillas como las llevadas a cabo por una puerta lógica o un

sistema combinacional hasta complejos sistemas en un chip.Ciertos fabricantes

cuentan con FPGAs que sólo se pueden programar una vez, por lo que sus ventajas

e inconvenientes se encuentran a medio camino entre los ASICs y las FPGAs

reprogramables.

Las FPGAs se utilizan en aplicaciones similares a los ASICs sin embargo son más

lentas, tienen un mayor consumo de potencia y no pueden abarcar sistemas tan

complejos como ellos. A pesar de esto, las FPGAs tienen las ventajas de ser

reprogramables (lo que añade una enorme flexibilidad al flujo de diseño), sus

costes de desarrollo y adquisición son mucho menores para pequeñas cantidades

de dispositivos y el tiempo de desarrollo es también menor.

Matriz

lógica programable(PAL)

Una matriz lógica programable o PAL es un dispositivo diseñado

por la empresa Monolithic Memories (ahora adquirida por AMD) y ha sido sin duda

el circuito programable más utilizado durante décadas.

La estructura de una PAL, derivada de las PLA, se basa en que cualquier función

lógica puede ser descrito por sumas de productos lógicos. Un dispositivo PAL

tiene una matriz de entrada formada por una puerta AND conectada a una serie de

puertas AND, con las salidas conectadas a un pin del dispositivo. La matriz de

puertas AND es programable y, por tanto, permite efectuar el producto lógico

con cualquier combinación de las entradas primarias.

Dispositivos

logicos programables simples(SPLD)

Los SPLDs es una combinación de un dispositivo lógico (arreglo

de compuertas AND, seguido por otro arreglo de compuertas OR, uno o ambos

arreglos programables, algunos incluyen Flip Flops) y una memoria. La memoria

se utiliza para almacenar el patrón el que se le ha dado al chip durante la

programación. La mayoría de los métodos para almacenar datos en un circuito

integrado han sido adaptados para el uso en SPLDs. Entre estos se incluyen:

antifusibles de silicio, SRAMs, Células EPROM o EEPROM y memoria flash.

Dispositivos SPLD se introducen en 1978 por Monolithic Memories, Inc., (MMI),

la arquitectura era más sencilla que la FPLA porque omitía la matriz OR

programable. Esto hizo los dispositivos más rápidos, más pequeños y más

baratos.

Los SPLD de MMI pronto fueron distribuidos por AMD la cual empleo tecnología

PROM de fusibles Titanio-Tungsteno programables una sola vez; Texas Instruments

apoya las PALs con arquitectura variable programables una sola vez y National

Semiconductor, quien fue el pionero en el desarrollo de Arreglos Lógicos

Programables (Programmable Logic Arrays, PLA’s) en forma de un DIP grande de 24

pines o terminales (0.6 pulgadas de ancho) con 96 términos productos, 14

entradas, 8 salidas.

jueves, 7 de octubre de 2021

Álgebra boole

El álgebra de Boole está formada por un conjunto de variables Booleanas,

x∈{0,1} y eso se basa en variables que sólo pueden tomar dos valores: 0 ó 1, abierto o cerrado, encendido o apagado, etc.

Un literal l es una variable o su negada. Existen dos tipos: literalres con signo positivo cuando representan el valor ‘1’ de la variable (l=x), y con signo negativo cuando representa el valor ‘0’ (l=¯¯¯x).

El álgebra de Boole está definido por 3 operaciones básicas: complemento, suma (OR) y producto (AND).

martes, 5 de octubre de 2021

Mapa de Karnaugh

Un mapa de Karnaugh (también conocido como tabla de Karnaugh o diagrama de Veitch) es un diagrama utilizado para la simplificación de funciones algebraicas en forma canónica. A partir de la tabla de Karnaugh se puede obtener una forma canónica mínima (con el mínimo número de términos). En este texto emplearemos indistintamente los términos “mapa” y “tabla” de Karnaugh.

La tabla de Karnaugh consiste en una representación bidimensional de la función que se quiere simplificar. Si la función viene expresada como una tabla de verdad, entonces la tabla de Karnaugh puede verse como una forma alternativa de representación 2D. Puesto que la tabla de verdad de una función de n variables posee 2n filas, la tabla de Karnaugh correspondiente debe poseer también 2n celdas. La construcción de la tabla de Karnaugh pasa por codificar cada celda en código binario reflejado (o código Gray) de manera que celdas adyacentes tengan un código que difiere en un solo dígito.

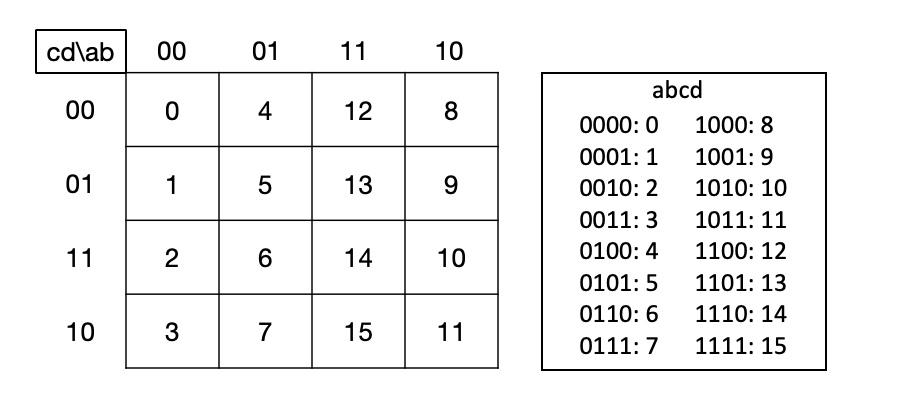

Figura 3.1: Descripción del mapa de Karnaugh

En la Fig. 3.1 puede verse un ejemplo de codificación Gray para el caso de funciones lógicas de 4 variables. Cada variable lógica (A, B, C, D en la figura) se corresponde con un bit del código Gray.

En la práctica, no es necesario explicitar el código de cada celda; basta con expresar las cabeceras de las filas y columnas en código Gray (el código de la celda se construye combinando la fila y columna correspondiente), según se desprende de la figura.

Definida la codificación Gray para la tabla, las celdas se rellenan asignando el valor ‘1’ para el caso que exista el término canónico correspondiente en la función objeto de análisis, y el valor ‘0’ en caso contrario. Si la función lógica viene expresada como tabla de verdad, se puede elegir la forma canónica para expresar la función. El criterio más lógico es elegir aquella forma que contenga inicialmente el menor número de términos. Para ello basta con contar el número de interpretaciones que satisfacen la fórmula lógica (filas de la tabla de verdad con resultado ‘1’). Cuando el número de interpretaciones que satisfacen la fórmula lógica es menor que el número de interpretaciones que no la satisfacen, se elige la forma canónica DNF. En caso contrario la CNF.

Una vez construida la tabla de Karnaugh se procede a la reducción del número de términos (si es posible) mediante la agrupación de celdas adyacentes en la tabla con valor ‘1’24.

Las dos secciones siguientes describen el algoritmo de simplificación en detalle para las formas canónicas DNF y CNF.

domingo, 3 de octubre de 2021

Dispositivos de programación

Dispositivos programables

Existes diferentes tipos de dispositivos el cual son (PAL,GAL,CPLD,FPGA)

Los PAL

Se basan en dispositivos para cualquier función lógica pueden ser descrita por sumas de producto, cuenta con una matriz de entrada formada por compuertas AND conectadas a una serie de puertas OR, con salidas que conectan a un pin del dispositivo

Los( CPLD)

Este tipo de dispositivos permiten implementar un sistema más eficaz ya que utilizan menor espacio mejorando la fiabilidad del diseño y reducen costos. CPLD se forman con múltiples bloques lógicos se comunican entre si utilizados una matriz programables de interconexiones

FPGA

Estos dispositivos semiconductores que contienen bloques de lógica conexión y estooa pueden ser programables mediante un lenguaje de descripción especializado. La lógica programable puede producir desde funciones sencillas como las llevamos por una puerta lógica

GAL

se Demonia a un circuito integrado que básicamente está formado por una matriz AND reprogrammable y una matriz OR fija con configuración de salidas y las entradas

Modulos embebidos DSP

Componentes de un sistema embebido Un estaría formando por un microprocesador y un software que se ejecute sobre éste. Sin embargo este...

-

Un mapa de Karnaugh (también conocido como tabla de Karnaugh o diagrama de Veitch) es un diagrama utilizado para la simplificación de fun...

-

import scipy.integrate as integrate import matplotlib.pyplot as plt import numpy as np pi=np.pi sqrt=np.sqrt cos=np.cos sin=np.s...

-

Frecuencia natural Cualquier objeto oscilante tiene una 'frecuencia natural', que es la frecuencia con la que tiende a vibrar lueg...